International Journal of Advanced Research in Computer and Communication Engineering Vol. 4, Issue 5, May 2015

# Design and Implementation of UART

Miss. Ruchika Longadge<sup>1</sup>, Prof. Mithilesh Mahindra<sup>2</sup>, Prof. Vidya Dahake<sup>3</sup>

Student, E&TC, AGPCOE, Nagpur, India<sup>1</sup>

Assistant Professor, E&TC, AGPCOE, Nagpur, India<sup>2</sup>

Assistant Professor, E&TC, AGPCOE, Nagpur, India<sup>3</sup>

Abstract: The proposed paper illustrate of UART using technique for implementation of UART using FIFO with the help of VHDL description language. The UART is protocol which is transmitted the information or data in serial form i.e. in serial communication mode. A special computer chip known as a universal asynchronous receiver transmitter acts as the interface between the parallel transmission of the computer bus and the serial transmission of the serial port.

Keywords: UART, RS-232, FIFO, VHDL IMPLEMENTATION ISE SIMULATOR 13.1.

#### I. **INTRODUCTION**

a kind of serial communication protocol. In serial transmission can be either synchronous or asynchronous .In synchronous transmission groups of bit are combined into frame and frame are send continuously with or without data to be transmitted. In asynchronous received from a peripheral device or a MODEM, and transmission groups of bits are sent as independent unit parallel-to-serial conversion on data characters received with start/stop flags and no data link synchronization to from the CPU. allow for arbitrary size gap between frames.

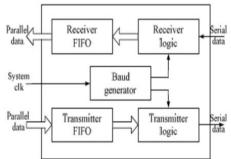

The UART (universal asynchronous receiver transmitter) are connected to the input of RS232 and the output if RS232 are connected to the FIFO (first in first out). The UART consist of three main components namely transmitter, receiver, baud rate generator.RS-232 are serial transmission via RS-232 is officially limited to 20kbps for a distance of 15 meter or 50 feet. Depending of the type of media used and the amount of external interference present RS-232 can be transmitted at higher speed or over Provisions are also included to use this 16 c clock to drive greater distance or both.

Baud rate of a data communication system is the number of symbols per second transferred. A symbol may have more than two states, so it may represent more than one binary bit. Therefore the baud rate is not equal to the bit rat. FIFO stand for first in first out meaning that the oldest inventory items are recorded as sold first but do not necessarily mean that the exact oldest physical object has been tracked and sold.

# A. UART

#### П. SYSTEM MODEL

The UART used asynchronous transmission. The asynchronous transmission means group of bit are sent as independent unit with start/stop flag and no data link synchronization. The UART controller is the key component of the serial communication subsystem of a computer. The UART takes bytes of data and transmits the individual bits in a sequential fashion. At the destination a second UART reassembles the bit into complete bytes.

In this mode internal FIFOs are activated allowing 16 bytes (plus 3 bits of error data per byte in the RCVR

Universal Asynchronous Receiver Transmitter (UART) is FIFO) to be stored in both receive and transmit modes. All the logic is on chip to minimize system overhead and maximize system efficiency. Two pin functions have been changed to allow signalling of DMA transfers. The UART performs serial-to-parallel conversion on data characters

> The CPU can read the complete status of the UART at any time during the functional operation. Status information reported includes the type and condition of the transfer operations being performed by the UART, as well as any error conditions (parity, overrun, framing, or break interrupt). The UART includes a programmable baud rate generator that is capable of dividing the timing reference clock input by divisors of 1 to (216b1), and producing a 16 c clock for driving the internal transmitter logic. the receiver logic. The UART has complete MODEMcontrol capability, and a processor- interrupt system. Interrupts can be programmed to the user's requirements, minimizing the computing required to handle the communications link.

Fig. 1. Basic configuration if UART with FIFO

#### **PROPOSED MODEL** III.

### A. UART FRAME FORMAT

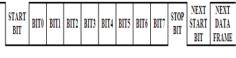

Below is the timing diagram for the transmission of a single bytes. Uses a single wire for transmission. Each block represents a bit that can be a mark (logic '1' high) or

### International Journal of Advanced Research in Computer and Communication Engineering Vol. 4, Issue 5, May 2015

space (logic '0'low). Each bit has a fixed time duration determined by transmission rate. The start bit marks the beginning of a new word. When detected the receiver synchronizes with the new data strum. Next follows the data bit (7 or 8). The least significant bit is sent first.

In the above frame format the above frame start the bit start bit . After start bit transmitted the 8 bit data and stop bit. In this type the one complete 8 bit data are transmitted. This 10 bit is transmitted then again the next start bit is transmitted and after 8 bit and stop bit and so on.

# B. BAUD RATE

Bit rate is a measure of the number of data bit (that's 0's and 1's) transmitted in one second. Baud rate by definition means the number of times a signal in a communications channel changes state. Baud means state changes of the line per second. Baud rate refers to the number of signal or symbols changes that occur per second.

A symbol is one of several voltage, frequency or phase changes. NRZ binary has two symbols represent voltage level.

Baud Rate represents the number of bits that are actually being sent over the media, not the amount of data that is actually moved from one UART device to the other. The Baud count includes the overhead bits Start, Stop and Parity that are generated by the sending UART and removed by the receiving UART.

This means that seven-bit words of data actually take 10 bits to be completely transmitted.

## **BAUD RATE** = NO OF BITS TRANSMITTED/ RECEIVER PER SECOND

Baud rate generator is used to generate the baud rate for both the transmitter and receiver. Not required for any other function including reads and writes. Crystal or external clock 16 bit divisor programmed in DLM/DLL registers. IN transmitter FIFO mode to write data to transmit holding register.

Transmit data is queued in TXFIFO. Data in TXFIFO is transferred to transmit shift register (TSR) when TSR is empty. TSR shift data out on TX output pin. The receiver FIFO incoming data is received in the receiver shift register (RSR) received data is queued in the RX FIFO.

## C. RS-232

A popular way to transfer commands and data between a personal computer and a Microcontroller is the use of standard interface, like the one described by protocols RS232 (older) or USB (newer). The protocol RS232 defines the signals used in communication, and the hardware to transfer signals between devices.

The standard defines voltage levels V(0) to be at least +5V at the transmitting end of the line TX, and can be degraded along the line to become at least +3V at the receiving and of the line. Similarly voltage level V (1) must be at least -5V at TX, and at least -3V at RX. The standard also defined the upper limit for these voltages to be up to  $\pm 15V$ . Logic high is transferred as V (0). The microcontroller cannot handle such voltage levels, so typically a voltage level translator is inserted between the microcontroller and the connector where the RS232 signals are available connectors are typically so-called D9 connectors, and the electric wiring in between two connectors at devices A and B is shown in Fig. for two female type connectors at both devices.

TABLE I: DEVICE UTILIZATION SUMMARY

| Logic utilization      | Used | Available | Utilization |

|------------------------|------|-----------|-------------|

| No of slice register   | 74   | 19200     | 0%          |

| No of slice LUT's      | 118  | 19200     | 0%          |

| No of fully used bit   | 71   | 121       | 58%         |

| No of bouded IOB's     | 27   | 220       | 12%         |

| No of<br>BUFG/BUFGCTRL | 1    | 32        | 3%          |

The whole design is functionally simulated using the Mentor Graphics company's Model Sim under 40MHz system clock and 9600Hz baud rate. As shown in Fig. the 8-bit data "11111111" is input from the transmitter port 'sbuf\_t', while "10010101" is serially output from the output port 'txd'; the data "11111111" is serially input from the receiver port 'rxd', while "1111111" is output from the function of the proposed design is right

| New Project Source Process Text Bet         |                                                                    |      |                             |              |                |         |        |   |           |

|---------------------------------------------|--------------------------------------------------------------------|------|-----------------------------|--------------|----------------|---------|--------|---|-----------|

| 10 0 X 0 0 X 10 0                           | REPAX                                                              | 8 2  | N:3-8 0 D: 2 42:00          | *            | 💌 : 🖓 : 🖬 G    | 7 8 8 T | 111100 |   |           |

| 2222 43380                                  | 8 22 14                                                            | 031  | 2 II 4a 5 p2 1000 Mai       | v            |                |         |        |   |           |

|                                             |                                                                    |      |                             |              |                | 52      | 5      |   |           |

| Behavioral Simulation                       | Now:<br>996 ns                                                     |      | 0 200                       |              |                |         |        |   |           |

| 10.9759                                     |                                                                    |      |                             |              |                |         |        |   |           |

| kooman<br>JAPITEST - similar (JAPITest-Ind) | and report                                                         | 0    |                             |              |                |         |        |   |           |

|                                             | <ul> <li>Citi</li> <li>Citi (Citi)</li> <li>Citi (Citi)</li> </ul> | 0    | , WARDON MANUNAL            |              |                |         |        |   |           |

|                                             | <ul> <li>Be cate (r t)</li> <li>Be cate (r t)</li> </ul>           | 3144 |                             |              |                |         |        |   |           |

|                                             | a de casadoria                                                     |      | _                           |              | 55             |         |        |   |           |

|                                             | A 10                                                               |      |                             |              |                |         |        |   |           |

|                                             | A 15.0                                                             |      | -                           |              |                |         |        |   |           |

|                                             | A 10.0                                                             |      |                             |              |                |         |        |   |           |

| 👩 Snapshots 🛛 Libraries                     | -                                                                  |      |                             |              |                |         |        |   |           |

|                                             |                                                                    |      |                             |              |                |         |        |   |           |

| UABTTCST - stimulus                         | A Provide                                                          |      |                             |              |                |         |        |   |           |

| to Existing Searce                          | · 24 ++++ (C                                                       | 210  | -                           |              |                |         | 151    |   |           |

| ende New Source                             |                                                                    |      | 1.00                        |              |                | _       |        |   |           |

| In TEE Similator<br>Oneck Surrise           |                                                                    |      |                             |              |                |         |        |   |           |

| Sender Syntax                               |                                                                    |      |                             |              |                |         |        |   |           |

|                                             |                                                                    |      |                             |              |                |         |        |   |           |

|                                             |                                                                    |      |                             |              |                |         |        |   |           |

|                                             |                                                                    |      |                             |              |                |         |        |   |           |

|                                             |                                                                    |      |                             |              |                |         |        |   |           |

|                                             | c 3                                                                |      |                             |              |                |         |        |   |           |

| m Ein Heardy-DARTTEST                       |                                                                    |      | RTaut-Ind III Senderon      |              |                |         |        |   |           |

|                                             |                                                                    | 1.00 | PTTBUE-M2                   |              |                |         |        |   |           |

| shed circuit initializatio                  | a process.                                                         |      |                             |              |                |         |        |   |           |

|                                             |                                                                    |      |                             |              |                |         |        |   |           |

| nde 🔕 Eron 🗼 Variege 📑                      | Tarthat De Daris De                                                |      | En Coucie - UNETTEST        |              |                |         |        |   |           |

| nis Taport (nini A07.ey)                    |                                                                    |      |                             |              |                |         |        |   | Tere: 177 |

|                                             | 🗅 unt, det Regending)                                              |      | un - Nordhal 🛛 📓 Minn - Ste | 100          | -19 - C'Osta   |         |        | _ | 0652 111  |

|                                             | on der Gernestenden.                                               |      | DELEMENT DELEMENT           | <b>2</b> 180 | - DE - C (2003 |         |        |   | 6.05.6    |

Fig. 4. The wave of UART function simulation

International Journal of Advanced Research in Computer and Communication Engineering Vol. 4, Issue 5, May 2015

# IV. CONCLUSION

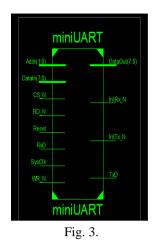

In this paper, we proposed a design of multi channel UART. It internally consists of baud rate generators, Asynchronous FIFO along with transmitters and receivers. The design is successfully simulated using xilinx ise 13.1 software and synthesized using Xilinx software. The results are stable and reliable which shows the correct functionality. Hope this multi channel design meet the modern communication needs. The design has great flexibility, high integration. Because of using FIFO data loss is avoid.

## REFERENCES

- [1]. Liu Weifeng, Zhuang Yiqi, Liu Feng, and He Wei, "Design of a high performance embedded UART," Chinese Journal Of Electron Devices, Vol. 30, No.4, pp.1275-1278, Aug 2007.

- [2]. R. J. Samuel, Self-tuning baud rate generator for UART applications, USA: 7062003B2, 2006.

- [3]. Himanshu Patel, Sanjay Trivedi, R.Neelkanthan, V. R. Gujraty " a robust uart architecture based on recursive running sum filter for better noise Performance".M. Wegmuller, J. P. von der Weid, P. Oberson, and N. Gisin, "High resolution fiber distributed measurements with coherent OFDR," in Proc. ECOC'00, 2000, paper 11.3.4, p. 109.

- [4]. Fang Yi-yaun and Chen Xue-jun, IEEE, 4, (2005).

- [5]. Dr. James. P. Davis, VLSI Design Lab, University of SouthCalifornia.

- [6]. Mohd. Yamani Idna Idris and Mashkuri Yaccob, Conference on convergent Technologies for Asia-Pacific Region,2003.

- [7]. Parul Sharma and Ashutosh Gupta, the IUP Journal of Science and Technology ,Vol 5, No. 4, pp. 21-30, December 2009.